오늘은 Megawizard로 PLL과 RAM구성을 해보도록 하겠다..

1. 먼저 Megawizard는 Tools > Megawizard plug-in manager로 동작시킬수 있다.

Megawizard는 간단히 설명하자면, Altera에서 제공하는 IP의 개념이다. 즉, 사용자가 altera에서 제공하는 IP들(PLL,RAM,ROM,... etc) 중에서 필요로 하는 IP를 불러서 내가사용하고자하는 형태로 Setting해주면 해당IP를 사용할수 있다.

2. 새로 만들려면, Create 선택후, 다음을 선택한다.

3. 왼쪽의 탐색기는 altera에서 제공하는 IP를 폴더 형태로 정리해놓은 것이다.

오른쪽 위에서 부터 사용하는 Device의 종류

사용하는 언어 선택.

생성할 IP의 폴더 위치 등을 선택할 수 있다.

4. PLL을 만들어 보겠다.

탐색창에서 IO폴더에 ALTPLL을 선택하고, 출력될 파일이름 PLL.v 형태로 작성후 next 선택.

5. ALTPLL을 선택후 다음을 누르면 다음과 같은 형태의 창이 생성된다.( Parameter Setting의 General/Modes) 이제 altera에서 제공하는 IP를 내입맛대로 setting하여 사용하면 된다.

기본적으로 빨간박스안의 내용을 사용하면되는데,

사용하는 Device의 속도를 선택하고, 입력clk의 속도를 입력하면된다. 50Mhz로 입력신호가 들어온다고 설정했다.

.

6. 입력과 출력Clock이외의 옵션들을 선택하여 회로에 응용할수 있다.(Input/Lock)

reset, locked신호등을 만들어서 사용할수 있다.(보통 locked신호를 출력신호로 만들어서, power on후, 신호가 안정화된후, 회로가 동작되도록 locked신호를 회로의 enable신호로 사용한다.)

7. bandwidth/SS, clock swichover는 따로 선택하지 않는다.

8. PLL reconfiguration도 따로 선택하지 않는다.

9. 출력할 clock의 갯수를 선택할수 있다. altpll의 경우, 5개까지 생성가능하다.

기본적으로 사용할 clk을 선택하고, 아래의 예시는 100Mhz의 clk을 생성하고, 50%의 clk duty cycle을 선택했다.

10. EDA sector는 simulation library의 이름을 알려준다.

나중에 simulation tool에서 altpll의 경우는 altera_mf 라는 library file이 필요하다는 설명이다.

11. summary sector는 출력될 파일에 대한 내용을 나타낸다.

보통 instantiation template file을 생성해서 쉽게 사용할수 있다.

이제 완료를 누르면 PLL이 생성된 것이다.

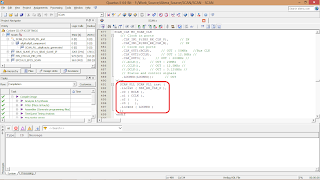

회로에 붙여넣기 위해서는 PLL_inst.v 파일을 보면 쉽게 사용할 수 있다.

실제 회로에서는 SCAN_PLL이라는 이름으로 PLL을 만들고, input clk1개에 4개의 출력clk을 생성했고, enable신호로 사용하기 위해 lock신호를 생성하였다.

해당 PLL을 simulation 한 결과이다.

필요한 clk을 생성하기 위해서는 PLL을 사용하여 변환시켜 사용하면 된다.

사실 좀더 자세히 작성할수도 있지만, 생각보다 화면캡쳐하고 글쓰고 하는게 번거로워서 이것 저것 많이 뛰어 넘은것도 있다.ㅠㅠ. 아무튼 PLL은 여기까지하고, 다음엔 RAM도 생성해보자.

사실, RAM이나 FIFO나 이런 것들은 altera 홈페이지에 사용법이 영어로 잘 설명되어 있다.

음.. 그러고 보니 굳이 내가 작성하지 않아도 되었네;;

아무튼, 다음에는 RAM생성해보고, simulation도 보여주고 음..

사실 pin 설정방법과 sdc file로 timing constraints 하는 방법등 할것이 엄청 많지만..

캡쳐의 번거로움이란..(1 Monitor의 한계라는 ㅠ_ㅠ)

아무튼, 천천히 진행해 보자..

'일 > Knowledge' 카테고리의 다른 글

| xilinx - Content-Addressable Memory ( CAM ) (0) | 2016.04.20 |

|---|---|

| xilinx - quad port ram (0) | 2016.04.20 |

| CRC verilog / VHDL (0) | 2016.04.15 |

| 압축 - 01 (0) | 2016.04.14 |

| Altera Quartus를 동작시키자(1장) (1) | 2016.04.10 |